VHDL Logical Operators and Signal Assignments for Combinational Logic

In this post, we discuss the VHDL logical operators, when-else statements , with-select statements and instantiation . These basic techniques allow us to model simple digital circuits.

In a previous post in this series, we looked at the way we use the VHDL entity, architecture and library keywords. These are important concepts which provide structure to our code and allow us to define the inputs and outputs of a component.

However, we can't do anything more than define inputs and outputs using this technique. In order to model digital circuits in VHDL, we need to take a closer look at the syntax of the language.

There are two main classes of digital circuit we can model in VHDL – combinational and sequential .

Combinational logic is the simplest of the two, consisting primarily of basic logic gates , such as ANDs, ORs and NOTs. When the circuit input changes, the output changes almost immediately (there is a small delay as signals propagate through the circuit).

Sequential circuits use a clock and require storage elements such as flip flops . As a result, changes in the output are synchronised to the circuit clock and are not immediate. We talk more specifically about modelling combinational logic in this post, whilst sequential logic is discussed in the next post.

Combinational Logic

The simplest elements to model in VHDL are the basic logic gates – AND, OR, NOR, NAND, NOT and XOR.

Each of these type of gates has a corresponding operator which implements their functionality. Collectively, these are known as logical operators in VHDL.

To demonstrate this concept, let us consider a simple two input AND gate such as that shown below.

The VHDL code shown below uses one of the logical operators to implement this basic circuit.

Although this code is simple, there are a couple of important concepts to consider. The first of these is the VHDL assignment operator (<=) which must be used for all signals. This is roughly equivalent to the = operator in most other programming languages.

In addition to signals, we can also define variables which we use inside of processes. In this case, we would have to use a different assignment operator (:=).

It is not important to understand variables in any detail to model combinational logic but we talk about them in the post on the VHDL process block .

The type of signal used is another important consideration. We talked about the most basic and common VHDL data types in a previous post.

As they represent some quantity or number, types such as real, time or integer are known as scalar types. We can't use the VHDL logical operators with these types and we most commonly use them with std_logic or std_logic_vectors.

Despite these considerations, this code example demonstrates how simple it is to model basic logic gates.

We can change the functionality of this circuit by replacing the AND operator with one of the other VHDL logical operators.

As an example, the VHDL code below models a three input XOR gate.

The NOT operator is slightly different to the other VHDL logical operators as it only has one input. The code snippet below shows the basic syntax for a NOT gate.

- Mixing VHDL Logical Operators

Combinational logic circuits almost always feature more than one type of gate. As a result of this, VHDL allows us to mix logical operators in order to create models of more complex circuits.

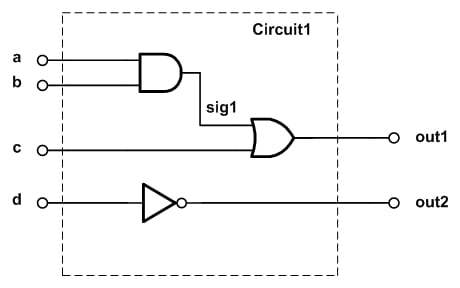

To demonstrate this concept, let’s consider a circuit featuring an AND gate and an OR gate. The circuit diagram below shows this circuit.

The code below shows the implementation of this circuit using VHDL.

This code should be easy to understand as it makes use of the logical operators we have already talked about. However, it is important to use brackets when modelling circuits with multiple logic gates, as shown in the above example. Not only does this ensure that the design works as intended, it also makes the intention of the code easier to understand.

- Reduction Functions

We can also use the logical operators on vector types in order to reduce them to a single bit. This is a useful feature as we can determine when all the bits in a vector are either 1 or 0.

We commonly do this for counters where we may want to know when the count reaches its maximum or minimum value.

The logical reduction functions were only introduced in VHDL-2008. Therefore, we can not use the logical operators to reduce vector types to a single bit when working with earlier standards.

The code snippet below shows the most common use cases for the VHDL reduction functions.

Mulitplexors in VHDL

In addition to logic gates, we often use multiplexors (mux for short) in combinational digital circuits. In VHDL, there are two different concurrent statements which we can use to model a mux.

The VHDL with select statement, also commonly referred to as selected signal assignment, is one of these constructs.

The other method we can use to concurrently model a mux is the VHDL when else statement.

In addition to this, we can also use a case statement to model a mux in VHDL . However, we talk about this in more detail in a later post as this method also requires us to have an understanding of the VHDL process block .

Let's look at the VHDL concurrent statements we can use to model a mux in more detail.

VHDL With Select Statement

When we use the with select statement in a VHDL design, we can assign different values to a signal based on the value of some other signal in our design.

The with select statement is probably the most intuitive way of modelling a mux in VHDL.

The code snippet below shows the basic syntax for the with select statement in VHDL.

When we use the VHDL with select statement, the <mux_out> field is assigned data based on the value of the <address> field.

When the <address> field is equal to <address1> then the <mux_out> signal is assigned to <a>, for example.

We use the the others clause at the end of the statement to capture instance when the address is a value other than those explicitly listed.

We can exclude the others clause if we explicitly list all of the possible input combinations.

- With Select Mux Example

Let’s consider a simple four to one multiplexer to give a practical example of the with select statement. The output Q is set to one of the four inputs (A,B, C or D) depending on the value of the addr input signal.

The circuit diagram below shows this circuit.

This circuit is simple to implement using the VHDL with select statement, as shown in the code snippet below.

VHDL When Else Statements

We use the when statement in VHDL to assign different values to a signal based on boolean expressions .

In this case, we actually write a different expression for each of the values which could be assigned to a signal. When one of these conditions evaluates as true, the signal is assigned the value associated with this condition.

The code snippet below shows the basic syntax for the VHDL when else statement.

When we use the when else statement in VHDL, the boolean expression is written after the when keyword. If this condition evaluates as true, then the <mux_out> field is assigned to the value stated before the relevant when keyword.

For example, if the <address> field in the above example is equal to <address1> then the value of <a> is assigned to <mux_out>.

When this condition evaluates as false, the next condition in the sequence is evaluated.

We use the else keyword to separate the different conditions and assignments in our code.

The final else statement captures the instances when the address is a value other than those explicitly listed. We only use this if we haven't explicitly listed all possible combinations of the <address> field.

- When Else Mux Example

Let’s consider the simple four to one multiplexer again in order to give a practical example of the when else statement in VHDL. The output Q is set to one of the four inputs (A,B, C or D) based on the value of the addr signal. This is exactly the same as the previous example we used for the with select statement.

The VHDL code shown below implements this circuit using the when else statement.

- Comparison of Mux Modelling Techniques in VHDL

When we write VHDL code, the with select and when else statements perform the same function. In addition, we will get the same synthesis results from both statements in almost all cases.

In a purely technical sense, there is no major advantage to using one over the other. The choice of which one to use is often a purely stylistic choice.

When we use the with select statement, we can only use a single signal to determine which data will get assigned.

This is in contrast to the when else statements which can also include logical descriptors.

This means we can often write more succinct VHDL code by using the when else statement. This is especially true when we need to use a logic circuit to drive the address bits.

Let's consider the circuit shown below as an example.

To model this using a using a with select statement in VHDL, we would need to write code which specifically models the AND gate.

We must then include the output of this code in the with select statement which models the multiplexer.

The code snippet below shows this implementation.

Although this code would function as needed, using a when else statement would give us more succinct code. Whilst this will have no impact on the way the device works, it is good practice to write clear code. This help to make the design more maintainable for anyone who has to modify it in the future.

The VHDL code snippet below shows the same circuit implemented with a when else statement.

Instantiating Components in VHDL

Up until this point, we have shown how we can use the VHDL language to describe the behavior of circuits.

However, we can also connect a number of previously defined VHDL entity architecture pairs in order to build a more complex circuit.

This is similar to connecting electronic components in a physical circuit.

There are two methods we can use for this in VHDL – component instantiation and direct entity instantiation .

- VHDL Component Instantiation

When using component instantiation in VHDL, we must define a component before it is used.

We can either do this before the main code, in the same way we would declare a signal, or in a separate package.

VHDL packages are similar to headers or libraries in other programming languages and we discuss these in a later post.

When writing VHDL, we declare a component using the syntax shown below. The component name and the ports must match the names in the original entity.

After declaring our component, we can instantiate it within an architecture using the syntax shown below. The <instance_name> must be unique for every instantiation within an architecture.

In VHDL, we use a port map to connect the ports of our component to signals in our architecture.

The signals which we use in our VHDL port map, such as <signal_name1> in the example above, must be declared before they can be used.

As VHDL is a strongly typed language, the signals we use in the port map must also match the type of the port they connect to.

When we write VHDL code, we may also wish to leave some ports unconnected.

For example, we may have a component which models the behaviour of a JK flip flop . However, we only need to use the inverted output in our design meaning. Therefore, we do not want to connect the non-inverted output to a signal in our architecture.

We can use the open keyword to indicate that we don't make a connection to one of the ports.

However, we can only use the open VHDL keyword for outputs.

If we attempt to leave inputs to our components open, our VHDL compiler will raise an error.

- VHDL Direct Entity Instantiation

The second instantiation technique is known as direct entity instantiation.

Using this method we can directly connect the entity in a new design without declaring a component first.

The code snippet below shows how we use direct entity instantiation in VHDL.

As with the component instantiation technique, <instance_name> must be unique for each instantiation in an architecture.

There are two extra requirements for this type of instantiation. We must explicitly state the name of both the library and the architecture which we want to use. This is shown in the example above by the <library_name> and <architecture_name> labels.

Once the component is instantiated within a VHDL architecture, we use a port map to connect signals to the ports. We use the VHDL port map in the same way for both direct entity and component instantiation.

Which types can not be used with the VHDL logical operators?

Scalar types such as integer and real.

Write the code for a 4 input NAND gate

We can use two different types of statement to model multiplexors in VHDL, what are they?

The with select statement and the when else statement

Write the code for an 8 input multiplexor using both types of statement

Write the code to instantiate a two input AND component using both direct entity and component instantiation. Assume that the AND gate is compiled in the work library and the architecture is named rtl.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Table of Contents

Sign up free for exclusive content.

Don't Miss Out

We are about to launch exclusive video content. Sign up to hear about it first.

- Network Sites:

- Technical Articles

- Market Insights

- Or sign in with

- iHeartRadio

Concurrent Conditional and Selected Signal Assignment in VHDL

Join our engineering community sign-in with:.

This article will review the concurrent signal assignment statements in VHDL.

This article will first review the concept of concurrency in hardware description languages. Then, it will discuss two concurrent signal assignment statements in VHDL: the selected signal assignment and the conditional signal assignment. After giving some examples, we will briefly compare these two types of signal assignment statements.

Please see my article introducing the concept of VHDL if you're not familiar with it.

Concurrent vs. Sequential Statements

To understand the difference between the concurrent statements and the sequential ones, let’s consider a simple combinational circuit as shown in Figure 1.

Figure 1. A combinational circuit.

If we consider the operation of the three logic gates of this figure, we observe that each gate processes its current input(s) in an independent manner from other gates. These physical components are operating simultaneously. The moment they are powered, they will “concurrently” fulfill their functionality. Note that while, in practice, the AND gate has a delay to produce a valid output, this does not mean that the OR gate will stop its functionality and wait until the output of the AND gate is produced. The OR gate will function all the time; however, its output will not be valid until its inputs have settled.

Now, let’s examine the VHDL description of Figure 1. This is shown below:

The main part that we are here interested in is the definition of the three gates:

Each of these lines describes a physical component in Figure 1. For example, the second line, which describes the OR gate, takes sig1 and c as inputs and produces the OR of these two values. We saw that the physical components of Figure 1 operate concurrently. Hence, it is reasonable to expect that the VHDL description of these gates should be evaluated in a concurrent manner. In other words, the above three lines of the code are executed at the same time and there is no significance to the order of these statements. As a result, we can rewrite the architecture section of the above code as below:

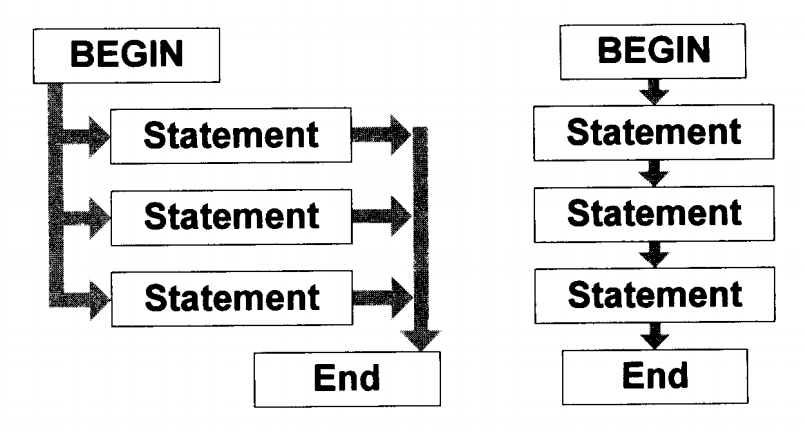

Since these statements are evaluated at the same time, we call them concurrent statements. This type of code is quite different from what we have learned in basic computer programming where the lines of code are executed one after the other. For example, consider the following MATLAB code:

This code produces out1=1 and out2=1 . However, if we change the order of the statements to the following, the program will stop working because we are trying to use sig1 before it is generated.

While the VHDL code describing Figure 1 was executed concurrently, the above MATLAB code is evaluated sequentially (i.e., one line after the other). VHDL supports both the concurrent statements and the sequential ones. It's clear that the concurrent VHDL statements will allow us to easily describe a circuit such as the one in Figure 1 above. In a future article, we'll see that the sequential VHDL statements allow us to have a safer description of sequential circuits. Furthermore, using the sequential VHDL, we can easily describe a digital circuit in a behavioral manner. This capability can significantly facilitate digital hardware design.

The following figure illustrates the difference between concurrent and sequential statements.

Figure 2. The difference between concurrent and sequential statements. Image courtesy of VHDL Made Easy .

Now let's take a look at two concurrent signal assignment statements in VHDL: “the selected signal assignment statement” and “the conditional signal assignment statement”.

Selected Signal Assignment or the “With/Select” Statement

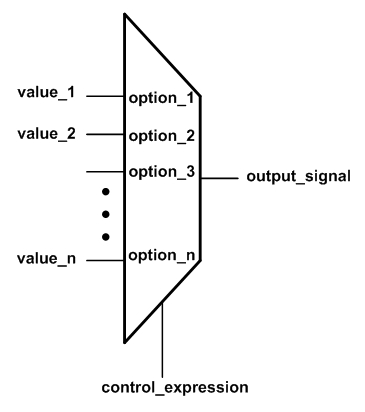

Consider an n -to-one multiplexer as shown in Figure 3. This block should choose one out of its n inputs and transfer the value of this input to the output terminal, i.e., output_signal .

Figure 3. A multiplexer selects one of its n inputs based on the value of the control_expression.

The selected signal assignment allows us to implement the functionality of a multiplexer. For example, the VHDL code describing the multiplexer of Figure 3 will be

Here, the value of the control_expression will be compared with the n possible options, i.e., option_1 , option_2 , …, option_n . When a match is found, the value corresponding to that particular option will be assigned to the output signal, i.e., output_signal . For example, if control_expression is the same as option_2 , then value_2 will be assigned to the output_signal .

Note that the options of a “with/select” assignment must be mutually exclusive, i.e., one option cannot be used more than once. Moreover, all the possible values of the control_expression must be included in the set of the options. The following example clarifies these points.

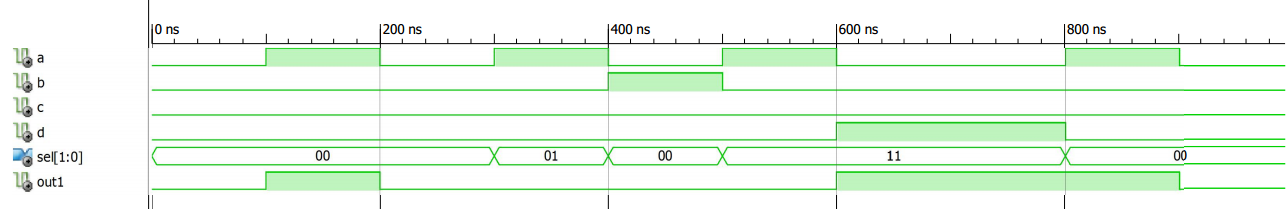

Example 1 : Use the "with/select" statement to describe a one-bit 4-to-1 multiplexer. Assume that the inputs to be selected are a , b , c , and d . And, a two-bit signal, sel , is used to choose the desired input and assign it to out1 .

The code for this multiplexer is given below:

Note that since the std_logic data type can take values other than “0” and “1” , the last line of the “with/select” statement needs to use the keyword “ others ” to take all the possible values of sel into account.

The following figure shows the simulation of this code using the Xilinx ISE simulator. (In case you’re not familiar with ISE, see this tutorial .) As shown in this figure, from 0 nanosecond (ns) until 300 ns the select input, sel , is 00, and, hence, out1 follows the input a . Similarly, you can verify the intended operation for the rest of the simulation interval.

Figure 4. The ISE simulation for the multiplexer of Example 1.

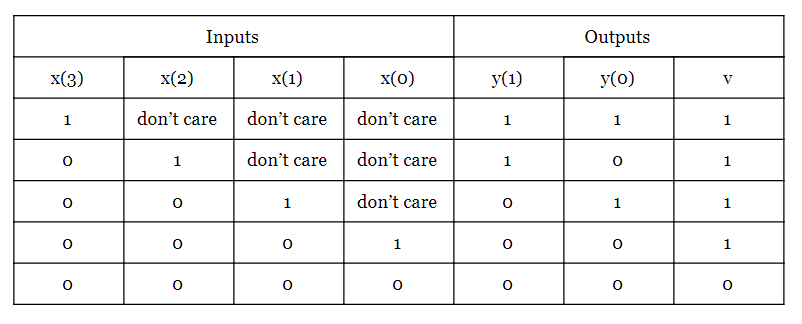

Example 2 : Use the “with/select” statement to describe a 4-to-2 priority encoder with the truth table shown below.

The following VHDL code can be used to describe the above truth table:

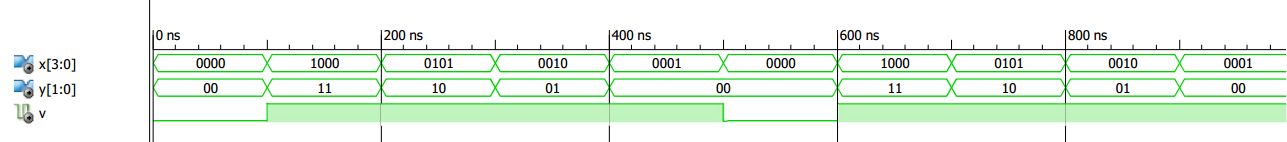

The ISE simulation is shown in Figure 5.

Figure 5. The ISE simulation for the priority encoder of Example 2.

Conditional signal assignment or the “when/else” statement.

The “when/else” statement is another way to describe the concurrent signal assignments similar to those in Examples 1 and 2. Since the syntax of this type of signal assignment is quite descriptive, let’s first see the VHDL code of a one-bit 4-to-1 multiplexer using the “when/else” statement and then discuss some details.

Example 3 : Use the when/else statement to describe a one-bit 4-to-1 multiplexer. Assume that the inputs to be selected are a , b , c , and d . And, a two-bit signal, sel , is used to choose the desired input and assign it to out1 .

The code will be

In this case, the expressions after “when” are evaluated successively until a true expression is found. The assignment corresponding to this true expression will be performed. If none of these expressions are true, the last assignment will be executed. In general, the syntax of the “when/else” statement will be:

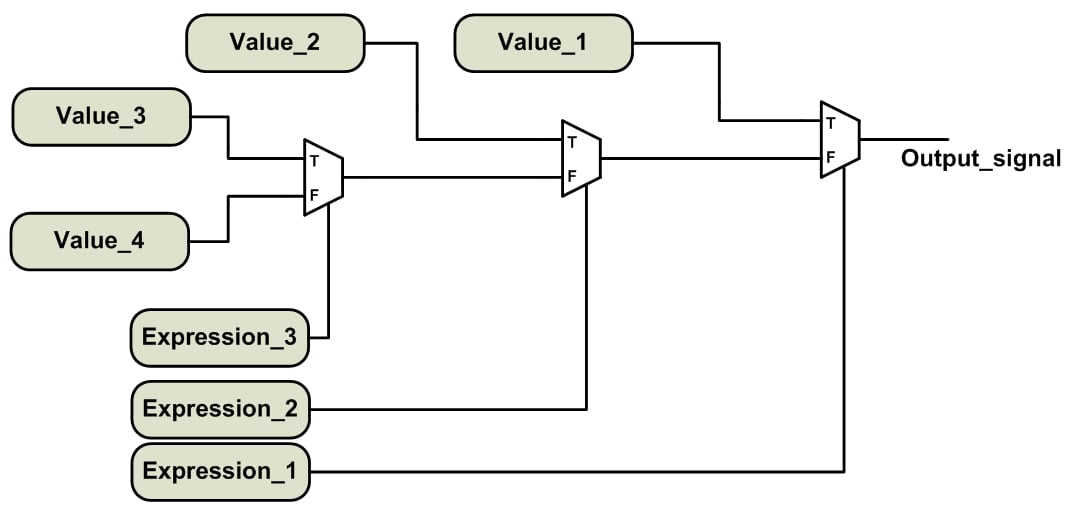

We should emphasize that the expressions after the “when” clauses are evaluated successively. As a result, the expressions evaluated earlier has a higher priority compared to the next ones. Considering this, we can obtain the conceptual diagram of this assignment as shown in Figure 6. This figure illustrates a conditional signal assignment with three “when” clauses.

Figure 6. The conceptual implementation of a “when/else” statement with three “when” clauses.

Let’s review the main features of the selected signal assignment and the conditional signal assignment.

“With/Select” vs. “When/Else” Assignment

As mentioned above, the options of a “with/select” assignment must be mutually exclusive, i.e., one option cannot be used more than once. Moreover, all the possible values of the control_expression must be included in the set of options. While the “with/select” assignment has a common controlling expression, a “when/else” assignment can operate on expressions with different arguments. For example, consider the following lines of code:

In this case, the expressions are evaluating two different signals, i.e., reset1 and clk .

For the “when/else” assignment, we may or may not include all the possible values of the expressions to be evaluated. For example, the multiplexer of Example 3 covers all the possible values of sel ; however, the above code does not. The above code implies that out1 should retain its previous value when none of the expressions are true. This causes the inference of a latch in the synthesized circuit.

Another important difference between the “with/select” and “when/else” assignment can be seen by comparing the conceptual implementation of these two statements. The priority network of Figure 6 involves a cascade of several logic gates. However, the “with/select” assignment avoids this chain structure and has a balanced structure. As a result, in theory, the “with/select” statement may have better performance in terms of the delay and area (see RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability , Xilinx HDL Coding Hints , and Guide to HDL Coding Styles for Synthesis ).

In practice, we generally don’t see this difference because many synthesis software packages, such as the Xilinx XST, try not to infer a priority encoded logic. Though we can use the PRIORITY_EXTRACT constraint of XST to force priority encoder inference, Xilinx strongly suggests that we use this constraint on a signal-by-signal basis; otherwise, the constraint may guide us towards sub-optimal results. For more details see page 79 of the XST user guide .

- Concurrent statements are executed at the same time and there is no significance to the order of these statements. This type of code is quite different from what we have learned in basic computer programming where the lines of code are executed one after the other.

- The selected signal assignment or the "with/select" assignment allows us to implement the functionality of a multiplexer.

- The options of a “with/select” assignment must be mutually exclusive, i.e., one option cannot be used more than once. Moreover, all the possible values of the control_expression must be included in the set of the options.

- For the "when/else" statement, the expressions after the “when” clauses are evaluated successively. As a result, the expressions evaluated earlier has a higher priority compared to the next ones.

- One important difference between the “with/select” and “when/else” assignment can be seen by comparing the conceptual implementation of these two statements. The "when/else" statement has a priority network; however, the “with/select” assignment avoids this chain structure and has a balanced structure.

To see a complete list of my articles, please visit this page .

Featured image used courtesy of Parallella .

Related Content

- Safety in Sensing: Sensor Technology in Smart Cities

- Thermocouple Signal Conditioners and Signal Conditioning Near the Cold Junction

- Reducing Distortion in Tape Recordings with Hysteresis in SPICE

- Test & Measurement in Quantum Computing

- Open RAN – Network Performance in the Lab and in the Field

- Looking for Good Waves: The Importance of Signal Integrity in High-Speed PCB Design

Learn More About:

- programmable logic

Great content. The link to the ISE guide requires password. Can we get that posted again? Thanks!

You May Also Like

Have You Heard?

In Partnership with AdvancedPCB

Researchers Advance Thermal Imaging for Military, Medical Infrared Thermography

by Jake Hertz

Switch Roundup: New Devices Make Switches Smaller and Faster

by Aaron Carman

Diamagnetic, Paramagnetic, and Ferromagnetic Materials Explained

by Dr. Steve Arar

Applying IP Customization to Improve AI Chips: A Case Study

by C.H. Chien, Faraday Technology

Welcome Back

Don't have an AAC account? Create one now .

Forgot your password? Click here .

- Product Manual

- Knowledge Base

- Release Notes

- Tech Articles

- Screencasts

Signal Assignments in VHDL: with/select, when/else and case

Sometimes, there is more than one way to do something in VHDL. OK, most of the time , you can do things in many ways in VHDL. Let’s look at the situation where you want to assign different values to a signal, based on the value of another signal.

With / Select

The most specific way to do this is with as selected signal assignment. Based on several possible values of a , you assign a value to b . No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment .

When / Else Assignment

The construct of a conditional signal assignment is a little more general. For each option, you have to give a condition. This means that you could write any boolean expression as a condition, which give you more freedom than equality checking. While this construct would give you more freedom, there is a bit more redundancy too. We had to write the equality check ( a = ) on every line. If you use a signal with a long name, this will make your code bulkier. Also, the separator that’s used in the selected signal assignment was a comma. In the conditional signal assignment, you need the else keyword. More code for the same functionality. Official name for this VHDL when/else assignment is the conditional signal assignment

Combinational Process with Case Statement

The most generally usable construct is a process. Inside this process, you can write a case statement, or a cascade of if statements. There is even more redundancy here. You the skeleton code for a process (begin, end) and the sensitivity list. That’s not a big effort, but while I was drafting this, I had put b in the sensitivity list instead of a . Easy to make a small misstake. You also need to specify what happens in the other cases. Of course, you could do the same thing with a bunch of IF-statements, either consecutive or nested, but a case statement looks so much nicer.

While this last code snippet is the largest and perhaps most error-prone, it is probably also the most common. It uses two familiar and often-used constructs: the process and the case statements.

Hard to remember

The problem with the selected and conditional signal assignments is that there is no logic in their syntax. The meaning is almost identical, but the syntax is just different enough to throw you off. I know many engineers who permanenty have a copy of the Doulos Golden Reference Guide to VHDL lying on their desks. Which is good for Doulos, because their name gets mentioned all the time. But most people just memorize one way of getting the job done and stick with it.

- VHDL Pragmas (blog post)

- Records in VHDL: Initialization and Constraining unconstrained fields (blog post)

- Finite State Machine (FSM) encoding in VHDL: binary, one-hot, and others (blog post)

- "Use" and "Library" in VHDL (blog post)

- The scope of VHDL use clauses and VHDL library clauses (blog post)

Select Statement – VHDL Example

Assigning signals using selected signal assignment.

Select statements are used to assign signals in VHDL. They can only be used in combinational code outside of a process . A selected signal assignment is a clear way of assigning a signal based on a specific list of combinations for one input signal. The syntax is demonstrated in the example below. The signal name after with is the signal whose values are used to assign the output signal. The when others clause should always be used to avoid creating a latch by accident.

Note that if you try to put a select statement inside a process, you will get the error: Illegal sequential statement.

Learn Verilog

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Difference between Blocking and Non-Blocking assignment in VHDL

I started reading about Blocking and Non-bocking assignment with reference to verilog. But when I switched to VHDL its confusing.

What I felt is, in VHDL other than to visually differentiate variable and signal assignment there is no significance for blocking and non-blocking assignment. Am I wrong?

2 Answers 2

Throw out the terms blocking and non-blocking assignments altogether, they have no place in VHDL. For which I am glad, they seem to cause enough confusion in Verilog.

The one huge advantage VHDL has over not just Verilog but virtually every other digital simulation/verification language out there is its deterministic timing model. In Verilog, simulations may legitimately deliver different results on different simulators because of the order in which processes (tasks, modules) are executed. Can't happen with VHDL - or if it does, there's a bug in the simulator.

But it's worth understanding how this timing model works - I'd say it's absolutely key to understanding VHDL. Grasp this and VHDL will become a lot easier.

It relies on 2 key points:

- There are only variable assignments and signal assignments, the latter are also known as postponed assignments.

- Time passes in infinitely short slices called "delta cycles" until nothing is happening, when it can step forward some finite timestep (fs, ps, ns) to the next scheduled event (delay, or clock edge).

Variables are local to a process, and variable assignments take place immediately - the next statement sees the new value.

Signal assignments don't happen immediately, but are scheduled to happen after the end of the current delta cycle , when all executing processes have happened. More detail here .

If it still isn't clear, refine the question.

Blocking/Non-blocking is a Verilog thing and at this level, it is best to learn VHDL without doing any association of these items.

If you must, however, variable assignments update immediately, and hence, are a little like blocking assignments. However, variable assignments are always local to a process, and hence, we don't need to worry about that set of race conditions. In addition, variables never have a delay.

Signals update either after a simulation cycle or a specified delay. So perhaps this is a little like Verilog's non-blocking assignment. The delay in VHDL only applies to when the signal is scheduled relative to the current process time and never impacts the process time. Time in a process only advances due to stopping at a sensitivity list or due to a wait statement. And a process never has both a sensitivity list and a wait statement.

Again they are different enough to warrant learning how VHDL's signals and variables work independent of how Verilog's blocking and non-blocking assignments.

- 2 \$\begingroup\$ "Signals update either after a simulation cycle or a specified delay. So perhaps this is a little like Verilog's blocking assignment" Here u meant Non-blocking right ? \$\endgroup\$ – tollin jose Commented Aug 26, 2015 at 12:47

- \$\begingroup\$ @tollin - Thanks. Yes I meant non-blocking. So my brain twists when I am up too late. \$\endgroup\$ – Jim Lewis Commented Aug 26, 2015 at 15:19

- \$\begingroup\$ Jim, is there a plan to allow VHDL to access SystemVerilog module internal signals used "external names"? \$\endgroup\$ – quantum231 Commented Feb 23, 2022 at 21:16

- \$\begingroup\$ Have you tried it? Cross language things are not defined by the language, however, your simulator probably implements it. \$\endgroup\$ – Jim Lewis Commented Feb 25, 2022 at 16:18

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged vhdl code or ask your own question .

- The Overflow Blog

- From PHP to JavaScript to Kubernetes: how one backend engineer evolved over time

- Where does Postgres fit in a world of GenAI and vector databases?

- Featured on Meta

- We've made changes to our Terms of Service & Privacy Policy - July 2024

- Bringing clarity to status tag usage on meta sites

Hot Network Questions

- Immutability across programming languages

- Why are most big lakes in North America aligned?

- Will this be the first time that there are more people aboad the ISS than seats in docked spacecraft?

- Can a rope thrower act as a propulsion method for land based craft?

- Meaning of “ ’thwart” in a 19th century poem

- Routing radiused edges between nodes in TikZ

- Stealth Mosquitoes?

- ApiVersion 61.0 changes behaviour of inheritance (cannot override private methods in inner class)

- In the tunneling effect, to find a particle inside the barrier must I necessarily supply energy to the particle?

- What are the limits of Terms of Service as a legal shield for a company?

- Amount Transfer Between Different Accounts

- Can I retain the ordinal nature of a predictor while answering a question about it that is inherently binary?

- Perfect squares cross-number

- How to justify our beliefs so that it is not circular?

- Submitting a paper as a nonacademic practitioner in a field

- Dress code for examiner in UK PhD viva

- Order of connection using digital multimeter wall outlet

- Are quantum states like the W, Bell, GHZ, and Dicke state actually used in quantum computing research?

- Are there any theoretical reasons why we cannot measure the position of a particle with zero error?

- What does "garb" mean in this passage?

- add images in \longtable and remove justification

- Why does my PC take a long time to start, then when it's at the login screen it jumps to the desktop instantly?

- Why do National Geographic and Discovery Channel broadcast fake or pseudoscientific programs?

- Where did Geordi's eyes go?

- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Advertising & Talent Reach devs & technologists worldwide about your product, service or employer brand

- OverflowAI GenAI features for Teams

- OverflowAPI Train & fine-tune LLMs

- Labs The future of collective knowledge sharing

- About the company Visit the blog

Collectives™ on Stack Overflow

Find centralized, trusted content and collaborate around the technologies you use most.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Get early access and see previews of new features.

VHDL difference between => and <=

I keep forgetting and its difficult to search for the answer in a textbook or the Internet.

- I am not referring to greater/less than or equal to btw. – Useless Intern Commented Nov 2, 2011 at 22:30

- Okay thanks guys I marked the accepted answer. In my context its for vector assignment but can be used for other things. – Useless Intern Commented Nov 2, 2011 at 23:13

- Does this answer your question? VHDL: signals and ports on which side of the "arrow" => – Henke - Нава́льный П с м Commented Mar 31, 2021 at 16:09

4 Answers 4

Well, <= is assignment.

=> is syntax used for case statements like so: (Stolen from http://www.cs.umbc.edu/portal/help/VHDL/sequential.html )

=> can also be used in array assignments

Source: http://www.eda.org/comp.lang.vhdl/html3/gloss_example.html

- Hmm that is close to the scenario but I encountered it while working with registers. SHould have stated that first D: ie: others=> (others=>'0') – Useless Intern Commented Nov 2, 2011 at 22:50

- Are you referring to vector assignments? I updated my answer. When working with vectors, you can use this operator to assign values to specific parts of the vector. – Akron Commented Nov 2, 2011 at 22:55

A means to memorize when to use => and when to use <= is to think as follow.

<= as an assignment for signal as target (for variable it is := ).

=> as mapping .

Example for component explicit mapping (recommended style IMHO):

Example for function explicit mapping (useful when parameters are not trivial):

Example for array explicit mapping

Example for record explicit mapping

The advantage is this style allows you to do the mapping in the order of your choice (not necessarily the order in the definition of the component/function...). Moreover in the particular case of array with only one item, it is required.

Finally, with the => , the keyword others allows to map all the remaining stuff that hasn't already mapped.

Example to assign array:

- The last example constant declaration is of an array type whose value is assigned the value of an array aggregate whose association elements provide the value through an association list . – user16145658 Commented Feb 14, 2023 at 15:50

<= represents the assignment operator while => is used in the case statement, for example:

sets line to "1" in case sel is "01" and to "0" otherwise.

=> is also used in structural code in port maps.

The operator <= is known as a signal assignment operator to highlight its true purpose. The signal assignment operator specifies a relationship between signals. In other words, the signal on the left side of the signal assignment operator is dependent upon the signals on the right side of the operator.

(Source: Digital_Mclogic_Design by Bryan Mealy, Section: The Signal Assignment Operator: “<=”, page 339)

I couldn't find anything specific on the => operator.

- Signal assignment is a basic operation and there is no signal assignment operator, it's in a signal assignment statement. The <= is just part of the syntax. See IEEE Std 1076. – user16145658 Commented Feb 14, 2023 at 15:40

Your Answer

Reminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more

Sign up or log in

Post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged syntax vhdl or ask your own question .

- The Overflow Blog

- From PHP to JavaScript to Kubernetes: how one backend engineer evolved over time

- Where does Postgres fit in a world of GenAI and vector databases?

- Featured on Meta

- We've made changes to our Terms of Service & Privacy Policy - July 2024

- Bringing clarity to status tag usage on meta sites

- Feedback requested: How do you use tag hover descriptions for curating and do...

- What does a new user need in a homepage experience on Stack Overflow?

- Staging Ground Reviewer Motivation

Hot Network Questions

- How to assess whether it is imposter syndrome or actual low quality work during Ph.D.?

- How can I see contents of maintainer scripts of apt packages?

- Why are volumes of revolution typically taught in Calculus 2 and not Calculus 3?

- Could a mini-Neptune host life at the surface with gas giant-style storms up above?

- Why doesn't the world fill with time travelers?

- Why do National Geographic and Discovery Channel broadcast fake or pseudoscientific programs?

- What can I do when someone else is literally duplicating my PhD work?

- Flight left while checked in passenger queued for boarding

- How do you determine what order to process chained events/interactions?

- How do you hide an investigation of alien ruins on the moon during Apollo 11?

- Which is the most convinent company to rent a car from at Copenhagen Airport

- What is the name of the book about a boy dressed in layers of clothes who is actually a mouse?

- How do I safely remove a mystery cast iron pipe in my basement?

- Is there any video of an air-to-air missile shooting down an aircraft?

- Are there different conventions for 'rounding to even'?

- Why are most big lakes in North America aligned?

- Submitting a paper as a nonacademic practitioner in a field

- How to justify our beliefs so that it is not circular?

- What' the intuition behind Shankar's postulate II?

- Order of connection using digital multimeter wall outlet

- The last person in Daniel 11. Who is it?

- My enemy sent me this puzzle!

- How much missing data is too much (part 2)? statistical power, effective sample size

- A simplified Blackjack C++ OOP console game

IMAGES

COMMENTS

The VHDL language allows several wait statements in a process. When used to model combinational logic for synthesis, a process may contain only one wait statement. If a process contains a wait statement, it cannot contain a sensitivity list. The process in Example 6.3, which contains an explicit wait statement, is equivalent to the process in ...

The VHDL code shown below uses one of the logical operators to implement this basic circuit. and_out <= a and b; Although this code is simple, there are a couple of important concepts to consider. The first of these is the VHDL assignment operator (<=) which must be used for all signals.

VHDL assignments are used to assign values from one object to another. In VHDL there are two assignment symbols: <= Assignment of Signals. := Assignment of Variables and Signal Initialization. Either of these assignment statements can be said out loud as the word "gets". So for example in the assignment: test <= input_1; You could say out ...

Conditional Signal Assignment or the "When/Else" Statement. The "when/else" statement is another way to describe the concurrent signal assignments similar to those in Examples 1 and 2. Since the syntax of this type of signal assignment is quite descriptive, let's first see the VHDL code of a one-bit 4-to-1 multiplexer using the ...

With / Select. The most specific way to do this is with as selected signal assignment. Based on several possible values of a, you assign a value to b. No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment. with a select b <= "1000" when "00", "0100" when "01", "0010" when "10 ...

Sequential statements model combinational or synchronous logic (or both) Statements within a process are 'executed' sequentially (but use care in interpreting this statement) Signal assignments can be both sequential and concurrent. 'Variables' may be declared within a process (more later) Signals must be a declared outside of the process.

Hardware Design with VHDL Concurrent Stmts ECE 443 ECE UNM 6 (9/6/12) Conditional Signal Assignment Statements Note that the use of std_logic data type, which has 9 possible values, makes the last statement assign d to x under more conditions than the expected s = "11" case In fact, since each bit of s can assume 9 values, there are actually 9*9 = 81 conditions ...

VHDL provides mainly two types/classes of statements that can be used to assign logic values to signals. • Concurrent Statements The term concurrent means that the VHDL statements are executed only when associated signals change value. There is no master procedural flow control, each concurrent statement executes when driven by an event. •

The outputs include a 2-bit signal (code), which is the binary code of the highest priority request and a 1-bit signal active that indicates if there is an active request. has the highest priority, i.e., when asserted, the other three requests are ignored and the code signal becomes "11". When r(3) is not asserted, the second highest request, r ...

Signal assignment statement 3. Variables are cheaper to implement in VHDL simulation since the evaluation of drivers is not needed. They require less memory. 4. Signals communicate among concurrent statements. Ports declared in the entity are signals. Subprogram arguments can be signals or variables. 5. A signal is used to indicate an ...

A conditional assignment statement is also a concurrent signal assignment statement. target <= waveform when choice; -- choice is a boolean expression target <= waveform when choice else waveform; sig <= a_sig when count>7; sig2 <= not a_sig after 1 ns when ctl='1' else b_sig; "waveform" for this statement seems to include [ delay_mechanism ...

The use of BLOCKs and GUARDs allows guarded targets to have their signal drivers disconnected (i.e. turned off) so that another concurrent signal assignment statement to the same target signal can determine the signal's value without the use of a VHDL Bus Resolution Function.

In VHDL-93, any signal assignment statement may have an optional label: label: signal_name <= expression; A delayed signal assignment with inertial delay may be explicitly preceded by the keyword inertial. It may also have a reject time specified. This is the minimum "pulse width" to be propagated, if different from the inertial delay:

The signal assignment statement is typically considered a concurrent statement rather than a sequential statement. It can be used as a sequential statement but has the side effect of obeying the general rules for when the target actually gets updated. In particular, a signal can not be declared within a process or subprogram but must be ...

Select statements are used to assign signals in VHDL. They can only be used in combinational code outside of a process. A selected signal assignment is a clear way of assigning a signal based on a specific list of combinations for one input signal. The syntax is demonstrated in the example below. The signal name after with is the signal whose ...

For writing the assignment in a single like, still use ; as statement separator, thus not , as shown in the question code, and then just remove the whitespace. The code is: ... For assign to multiple signals in one statement, the VHDL-2008 supports aggregate assignment, so if you are using VHDL-2008, you can write:

In VHDL-93, any signal assigment statement may have an optinal label. VHDL-93 defines an unaffected keyword, which indicates a condition when a signal is not given a new assignment: label: signal = expression_1 when condition_1 else expression_2 when condition_2 else unaffected ; The keywords inertial and reject may also be used in a ...

Time in a process only advances due to stopping at a sensitivity list or due to a wait statement. And a process never has both a sensitivity list and a wait statement. Again they are different enough to warrant learning how VHDL's signals and variables work independent of how Verilog's blocking and non-blocking assignments.

The statement "Others => '0'" is a feature of the VHDL when the coder want to defined several items in an array with the same value. In your example, all item std_logic in the array are set to '0'. Another application of this statement is to set some items at a specific value and all others at a default value : cmd_r <= (0 => '1', 4 => '1',

In the O0 assignment for instance two of the terms don't require i0 to be '1', yet you require i0 to be '1' in all four using a '1' choice in the selected assignment statement. You are not implementing the Boolean expressions you show before the VHDL code faithfully using a selected signal assignment and should implement them directly without the selected signal assignment as Brian suggests.

Signal assignment is a basic operation and there is no signal assignment operator, it's in a signal assignment statement. The <= is just part of the syntax. See IEEE Std 1076. - user16145658. Commented Feb 14, ... VHDL If Statements. 15. What' s the difference between <= and := in VHDL. 2. Using '<=' operator in verilog. 3.